Tales from the Cube: Stopped in our tracks Pg 54

**EDN.comment:** The time is now for 3-D stacked die Pg 9

Signal Integrity: Water analogy Pg 18

Design Ideas Pg 43

Supply Chain Pg 51

#### **EM SIMULATION FOR EMC:**

www.edn.com

Page 26

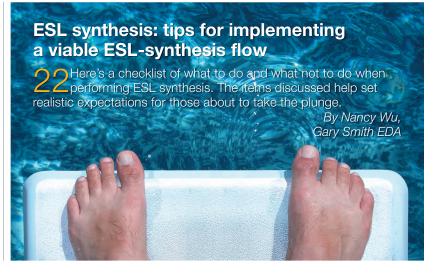

#### **ESL SYNTHESIS:**

TIPS FOR **IMPLEMENTING** A VIABLE ESL-SYNTHESIS FLOW

Page 21

#### **DESIGN QUALITY**

AND ITS IMPACT ON **DESIGN CLOSURE**

Page 33

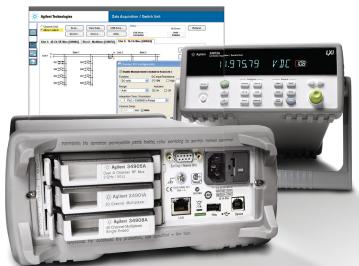

#### Data acquisition just got a lot easier.

#### More ways to control. More ways to connect.

The new Agilent 34972A Data Acquisition Switch Unit takes our best-selling Agilent 34970A to the next level. For starters, you get convenient built-in LAN and USB connectivity. Plus, you can control your data acquisition remotely via Web interface. And transfer logged data to your PC with a simple flash drive. No more expensive adapters and connectors. That's easy. That's Agilent.

| <b>NEW</b> 34972A                                                       | 34970A                                          |  |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| USB and LAN                                                             | GPIB and RS232                                  |  |  |  |  |

| Graphical web interface Benchlink data logger software SCPI programming | Benchlink data logger software SCPI programming |  |  |  |  |

| 3-slot LXI unit with built-in 6 ½ digit DMM                             |                                                 |  |  |  |  |

| \$4,845 \$1,597*                                                        | \$1,597*                                        |  |  |  |  |

Hurry! For a limited time, get the 34972A at the 34970A price. www.agilent.com/find/Agilent34972A

© 2010 Agilent Technologies, Inc.

\*Prices are in USD and are subject to change

See participating distributors for details.

Over 465,000 Products in Stock More Than 45,000 NEW Products Added in the Last 90 Days 440+ Suppliers

The industry's broadest product selection available for immediate delivery

www.digikey.com 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

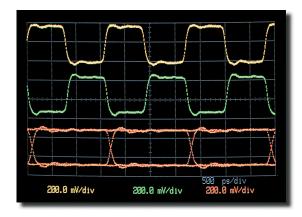

#### 2 GHz Clock Generator

CG635...\$2490 (U.S. list)

- Square wave clocks from DC to 2.05 GHz

- Random jitter <1 ps (rms)</li>

- · 80 ps rise and fall times

- · 16-digit frequency resolution

- · CMOS, LVDS, ECL, PECL, RS-485

- · Phase adjustment & time modulation

Plot shows complementary clocks and PRBS (opt. 01) outputs at 622.08 Mb/s with LVDS levels. Traces have transition times of 80 ps and jitter less than 1 ps (rms).

The CG635 generates clock signals—flawlessly. The clock signals are fast, clean and accurate, and can be set to standard logic levels.

**How fast?** Frequency to 2.05 GHz with rise and fall times as short as 80 ps.

How clean? Jitter is less than 1 ps and phase noise is better than -90 dBc/Hz (100 Hz offset) at 622.08 MHz.

How accurate? Using the optional rubidium timebase, aging is better than 0.0005 ppm/year, and temperature stability is better than 0.0001 ppm.

You would expect an instrument this good to be expensive, but it isn't. You no longer have to buy an rf synthesizer to generate clock signals. The CG635 does the job better—at a fraction of the cost.

**Stanford Research Systems**

## EDN 7,15,10 contents

#### **EM** simulation for EMC: keeping a lid on interference

Field-solver simulation can do your work, but you have to do the thinking.

By Paul Rako, Technical Editor

- 12 SMUs support testing of battery-powered products, system components

- 13 NI advances IEEE 802.11n WLAN test

- 13 IP block makes audio-bandwidth 12-bit ADC from digital logic

- 14 Low-power e-nose checks air quality

- 14 Tool gives early area, power, and timing estimates

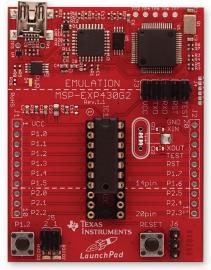

- 15 Open-source development board: \$4.30

- 16 Equivalent-time-sampling scope improves accuracy of characterizing high-speed designs

- 16 Seagate takes cautious approach to solid-state drives

#### Design quality and its impact on design closure

Steps to ensure quality early in the design can speed closure and avoid failed silicon.

By Piyush Sancheti and Sanjay Churiwala, Atrenta Inc., and Rob Knoth, Magma Design Automation

#### ESIGNIDEAS

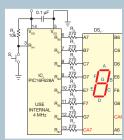

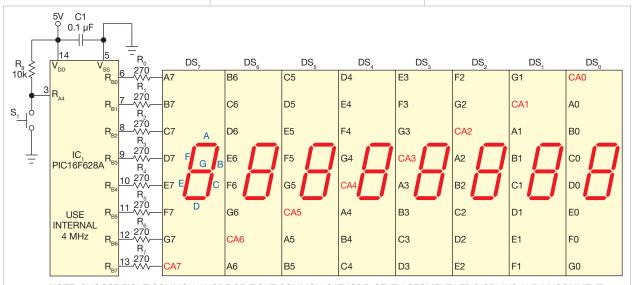

- 43 Eight-digit counter works with common anode or common cathode

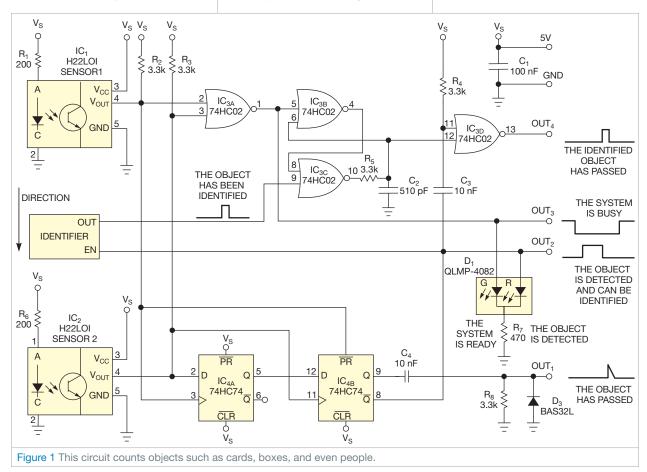

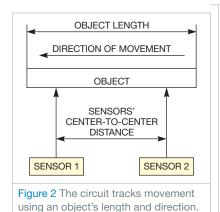

- 44 Count objects as they pass by

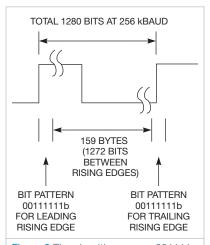

- 46 Modified DDS functions as baud-rate generator

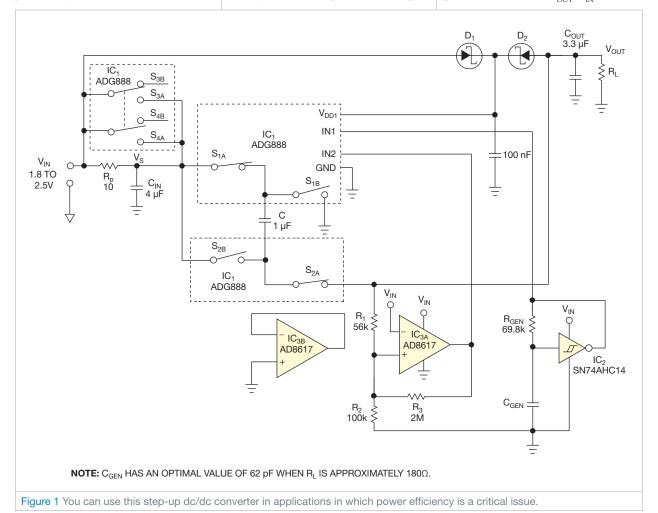

- 49 DC-voltage doubler reaches 96% power efficiency

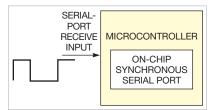

- 49 Microcontroller's serial port measures pulse width

## Better performance. Less effort.

Right out of the box, a better inductor for your aerospace/MIL applications.

Shorten your time-to-market and improve performance with surface-mount chip inductors from Coilcraft CPS. These robust COTS Plus devices are ready to load without further handling or processing...tested to meet your specs, directly from Coilcraft CPS.

ML Series inductors are designed, manufactured and tested to ensure their suitability for mission-critical applications under adverse environmental conditions. Alternate terminations, such as tin/lead, gold, and

leach resistant alloy are featured for long term reliability.

Compared to other 0603 inductors, the ML Series offers higher inductance values, to keep board space to a minimum.

- Inductance values range from 47nH–22μH

- Q ratings are as high as 50 at 250MHz with Self Resonant Frequencies to 16 GHz

- Ceramic construction provides high-current handling

- MTBF is an amazing 1 billion hours

Learn more about ML Series and other Coilcraft CPS magnetics by calling us or visiting www.coilcraft-cps.com today.

#### contents 7.15.10

#### **DEPARTMENTS & COLUMNS**

- 9 EDN.comment: The time is now for 3-D stacked die

- 18 Signal Integrity: Water analogy

- **Supply Chain:** Outsourced engineering services show solid growth; Gartner expects record semi sales this year

- 52 Product Roundup: Optoelectronics/Displays

- 55 Tales from the Cube: Stopped in our tracks

#### **EDN** online contents

www.edn.com

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Path-specific derating to reduce timing pessimism: a proposal

Reducing your pessimism about timing uncertainty as the design progresses can speed timing closure.

→www.edn.com/100715toca

#### The not-so-smart grid

What exactly are the standards for the next-generation utility grid? In many cases, nobody knows.

→www.edn.com/100715tocb

#### EUV lithography cannot come soon enough

Sematech's biennial Litho Forum survey shows that the cost of ownership is a leading concern as respondents anticipate their critical-layer lithography needs. Collaboration is key for bringing in viable solutions.

→www.edn.com/100715tocc

#### What's happening in the electronics world?

The EDN.com News Center provides real-time breaking news and analysis on the global electronics industry, including coverage of semiconductors, lawsuits, IC design, microprocessor units, consumer electronics, analog, and business trends.

→www.edn.com/100715tocd

#### **Exclusive e-book**

EDN's third "Designing with LEDs" event, held March 17, 2010, in Santa Clara, CA, addressed high-brightness-LED design challenges from the

viewpoint of the hardware engineer. Topics included power control, thermal management, and optics—all of which affect the cost, efficiency, and life span of LEDs. Six of the technical papers presented at the seminar are available in a downloadable e-book.

→www.edn.com/100715toce

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549, 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, California, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: U.S, \$150 one year, \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. Email: EDN@kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes Inc, PO Box 25542, London, ON N6C 682. Copyright 2010 by Canon Communications LLC. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 55, Number 13 (Printed in USA).

## Simpler Power Conversion

IR's AC-DC product portfolio offers simple, compact high density solutions tailored for energy-efficient power supplies.

#### µPFC™ PFC IC

| Part<br>Number     | Pckg.         | V <sub>cc</sub> (V) | Freq.<br>(kHz) | Gate<br>Drive<br>±(A) | V <sub>GATE</sub><br>Clamp<br>(V) | Current<br>Mode |

|--------------------|---------------|---------------------|----------------|-----------------------|-----------------------------------|-----------------|

| IR1150<br>(STR)PbF | SO-8<br>PDIP8 | 13-22               | 50-200         | 1.5                   |                                   | ССМ             |

| /                  |               |                     |                |                       |                                   |                 |

#### **SmartRectifier™ IC**

| _ | Part<br>Number                 | IR1166S<br>PbF | IR1167AS<br>PbF | IR1167BS<br>PbF | IR1168S<br>PbF |  |  |  |

|---|--------------------------------|----------------|-----------------|-----------------|----------------|--|--|--|

|   | Package                        |                |                 |                 |                |  |  |  |

|   | V <sub>cc</sub> (V)            |                |                 | 20              |                |  |  |  |

|   | V <sub>FET</sub> (V)           |                |                 | =200            |                |  |  |  |

|   | Sw Freq.<br>max (kHz)          |                | 500             |                 |                |  |  |  |

|   | Gate Drive<br>±(A)             | +1/-4          | +2              | +1/-4           |                |  |  |  |

|   | V <sub>GATE</sub> Clamp<br>(V) | 10.7           | 10.7            | 14.5            | 10.7           |  |  |  |

|   | Min. On Time<br>(ns)           | Р              | 750             |                 |                |  |  |  |

|   | Channel                        |                |                 |                 |                |  |  |  |

|   | RoHS                           | ~              |                 | ~               |                |  |  |  |

For more information call 1.800.981.8699 or visit

International Rectifier

THE POWER MANAGEMENT LEADER

Our engineers needed a scope with digital trigger to catch every glitch. So we built one.

#### BY RICK NELSON, EDITOR-IN-CHIEF

#### The time is now for 3-D stacked die

s the semiconductor industry moves from "more Moore" to "more than Moore," 3-D-stacked-die implementations will become critical for implementing ever-denser chip packages. Interest in the technology is strong, based on an over-flow crowd attending a June 16 DAC (Design Automation Conference) panel, "3-D stacked die—now or in the future?" The consensus seemed to be that the 3-D revolution is imminent. Panelist LC Lu of TSMC (Taiwan Semiconductor Manufacturing Co) said that his company is developing the TSV (through-silicon-via) technology that will interconnect the stacked chips in stacked die, with a focus on design, packaging, and testing—not just the fabrication process.

There are obstacles, however. Panelist Myung-Soo Jang of Samsung suggested that accurate design and analysis tools that work together in a seamlessly integrated flow could speed the adoption of 3-D implementations. Lu agreed that new design methods could help address challenges related to good-die sorting, process variations, and thermal and mechanical stress.

Manufacturers are making progress on the design-tool front. Atrenta, Auto-ESL, Qualcomm, and IMEC at DAC demonstrated a working prototype front-end 3-D chip-design system. The flow the companies demonstrated addresses 3-D-aware high-level synthesis, early partitioning, floorplanning, and multidomain analysis. "The daunting challenges of 3-D design demand a 3-D-aware high-level-synthesis approach," said Atul Sharan, president and chief executive officer of AutoESL.

"Early partitioning, floorplanning, and analysis yield substantial benefits for design predictability on conventional advanced SOCs," said Ravi Varadarajan, Atrenta fellow. "With the emergence of 3-D multitechnology design, this activity now becomes an absolute must-have. You simply cannot hand off

a 3-D design to back-end implementation without knowing for certain that it's partitioned correctly."

The demonstration grew out of what Riko Radojcic of Qualcomm called PathFinding technology, which Qualcomm has been developing over a number of years. According to

Radojcic, with traditional Moore's law process migration—from 90 to 65 nm, for example—it's relatively easy to project what will happen. The new geometry will yield devices that are smaller, faster, and more prone to leakage—information that can assist in building working and yielding parts.

Such projections aren't necessarily valid or helpful with 3-D parts. Something that allows you to explore knobs at both the architectural and the process ends is necessary, said Radojcic. "That's PathFinding to me." The collaboration with Atrenta, Auto-ESL, and IMEC, he added, is an effort to build a commercial set of tools that assist the PathFinding function.

Pol Marchal, principal scientist for IMEC's 3-D SOC-design initiative, who assisted with the June 14 demonstration, addressed PathFinding technology on June 8 at the IMEC Technology Forum at IMEC headquarters in Leuven, Belgium. IMEC's overall 3-D efforts, he said, involve investigations of TSV technology, wafer thinning and back-side processing, the packaging of 3-D die stacks, cost modeling, and 3-D system exploration, with the last being germane to PathFinding technology.

Marchal called PathFinding a systematic exploration of trade-offs. "Understanding the system requirements provides the engineer with inputs to guide design and technology decisions," he said, adding that a PathFinding flow allows engineers to iterate on design and technology choices to optimize footprint, timing, thermal performance, and other functions.

Marchal cited as an example a mobile consumer device, which would require three or four chip tiers with a package thickness of less than 0.6 mm and more than 1000 TSVs per tier operating at 400 MHz and providing a 12.8-Gbyte/sec data rate, all while consuming less

analysis, he said, shows the feasibility of building such a device.

than 2.5 pJ/bit. PathFinding

Despite the emergence of 3-D-design tools, obstacles will remain to the widespread adoption of 3-D techniques. DAC panelist Joe Adam of JMA Consulting predicted that incumbents with signals.

nificant investment in 2-D technologies will be reluctant to change.

Ultimately, however, resistance is futile. As IMEC's Marchal told the June 16 DAC panel attendees, "Practice today or don't play tomorrow." EDN

Go to the Talkback section at www. edn.com/100715ed to post a comment on this article.

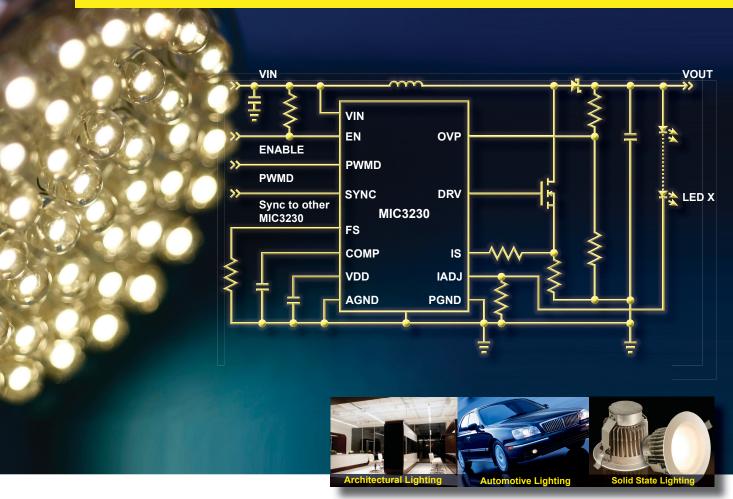

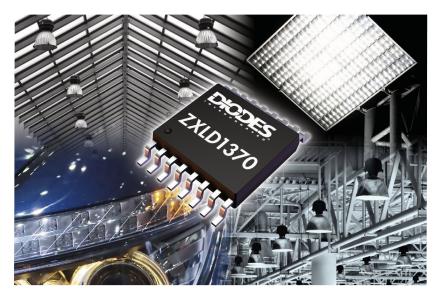

#### **Bringing the Power to Light™ with High Performance LED Drivers**

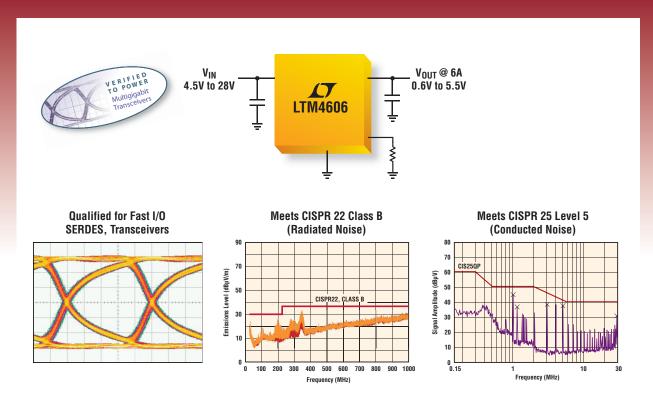

Wide Input Voltage, Low EMI, High Power LED Drivers. Easy to Use, Flexibility by Design.

The rapid growth of LED lighting applications in commercial, industrial and automotive markets has led to a wide variety of technical requirements for LED drivers. Micrel is meeting these challenges with its family of high performance LED drivers.

For example, the new 45V input, 70W, 3% accuracy constant current boost controllers like MIC3230/1/2 delivers the performance and flexibility needed. In addition to the PWM dimming and synchronization capability, these LED drivers also offer dither feature for EMI reduction up to 10dB thus providing an unparalleled performance for your solid state lighting applications.

For more information, contact your local Micrel sales representative or visit Micrel at: www.micrel.com/mic3230.

Ideal for use in:

- Solid State Lighting

- Street Lighting

- General Illumination

- Architectural Lighting

- Constant Current Power Supplies

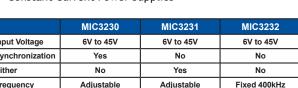

|                    | MIC3230                      | MIC3231                      | MIC3232      |

|--------------------|------------------------------|------------------------------|--------------|

| Input Voltage      | 6V to 45V                    | 6V to 45V                    | 6V to 45V    |

| Synchronization    | Yes                          | No                           | No           |

| Dither             | No                           | Yes                          | No           |

| Frequency<br>Range | Adjustable<br>100kHz to 1MHz | Adjustable<br>100kHz to 1MHz | Fixed 400kHz |

| Package            | 16-Pin TSSOP<br>12-Pin MLF®  | 16-Pin TSSOP<br>12-Pin MLF®  | 10-Pin MSOP  |

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-869-7982; russell.pratt@cancom.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@cancom.com

#### EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-869-7970; richard.nelson@cancom.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-510-744-1263; ronald, wilson@cancom.com

#### MANAGING EDITOR

Amy Norcross 1-781-869-7971; fax: 1-781-862-4853;

amy.norcross@cancom.com

Contact for contributed technical articles

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@cancom.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-548-1225; brian.dipert@cancom.com

#### **NEWS**

Suzanne Deffree, Managing Editor 1-631-266-3433; suzanne.deffree@cancom.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; margery.conner@cancom.com

#### **DESIGN IDEAS EDITOR**

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@cancom.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-781-862-4853; frances.granville@cancom.com

#### ASSOCIATE EDITOR

Jessica MacNeil jessica.macneil@cancom.com

#### CONSULTING EDITOR

Jim Williams, Staff Scientist, Linear Technology edn.editor@cancom.com

#### **CONTRIBUTING TECHNICAL EDITORS**

Dan Strassberg, strassbergedn@att.net Robert Cravotta, robert.cravotta@embeddedinsights.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

#### LEAD ART DIRECTOR

Marco Aguilera

#### ASSOCIATE ART DIRECTOR

Tim Burns

#### PRODUCTION

Michael Ciardiello,

Director of Premedia Technologies

Jeff Tade,

Production Director

Brian Wu,

Publications Production Manager

Jeff Polman, Derric Treece,

Senior Production Artists

William Baughman, Lucia Corona

Ricardo Esparza,

Production Artists

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

#### **EDN ASIA**

Wai-Chun Chen, Group Publisher, Asia waichun.chen@cancom.com Kirtimaya Varma, Editor-in-Chief kirti.varma@cancom.com

#### **EDN CHINA**

#### EDN JAPAN

Katsuya Watanabe, Publisher katsuya.watanabe@cancom.com Ken Amemoto, Editor-in-Chief ken.amemoto@cancom.com

#### **EXECUTIVE OFFICERS**

Charles G. McCurdy,

Chief Executive Officer

Fred Gysi,

Chief Financial Officer

Mike Deering,

Chief Technology Officer

Ron Wall,

Senior Vice President, Publications

Kevin O'Keefe,

Senior Vice President, Events Division

Roger Burg,

Vice President Operations

Vice President, Operations

Jason Brown,

Vice President, E-media

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change. Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

#### SMUs support testing of batterypowered products, system components

gilent Technologies has added two two-quadrant SMUs (source-measurement units) to its N6700 series of modular power systems—the N6781A for battery-drain analysis and the N6782A for functional test. The units, which perform as voltage or current sources or as constant-voltage or constant-current electronic loads, provide the advanced capabilities you need to test battery-powered devices and their components. The company also introduced software and updates for its dc-power-analyzer mainframe.

Thanks to the products' seamless measurement ranging, you can precisely view and measure dynamic-current waveforms without glitches or disruptions. The SMU automatically detects the current of the DUT (device under test) as it changes and switches among its four measurement ranges to the range that returns the most precise measurement.

In combination with the units' built-in 18-bit 200k-sample/sec digitizer, seamless measurement ranging enables 28-bit effective vertical resolution. In one pass and one picture, the units let you see complete current waveforms—from nanoamps to amperes. A complementary feature provides quick glitch-free transitions among source ranges.

When you use the N6781 with the manufacturer's 14585A software, the N6781A provides insights into the battery drain of e-book readers, music players, mobile phones, and pacemakers. The unit also includes an auxiliary DVM (digital voltmeter).

The N6782A can modulate its output to 100 kHz and provides two-quadrant operation, suiting it for such devices as dc/dc converters, power-management units, power ampli-

fiers, and power-management ICs. The fast sourcing and waveform capabilities can stimulate the DUT's input stage, and the electronic-load capabilities can load the output stage and measure its performance, thus enabling comprehensive testing.

The product family includes four mainframes and 24 dc-power modules, providing a range of configurations—from R&D through design validation and manufacturing. The updated N6705B dc-power analyzer has an internal memory of 1 Gbyte and fully supports the new modules, including modules that can output more than 20A.

The N6781A for battery-drain analysis, the N6782A for functional test, and the N6705B mainframe sell for \$5300, \$4230, and \$6900, respectively. A software license for the 14585A costs \$1240.—by Dan Strassberg

► Agilent Technologies Inc, www.agilent.com/find/n6780.

#### FEEDBACK LOOP

"I'm amazed that you kept old, dead PALs. I used them a bunch, too, and usually had a pile of old, dead PALs ... in a corner of my workbench. ... Your description certainly evoked those days for me."

—Engineer and former *EDN*Editor-in-Chief Steve Liebson, in *EDN's* Talkback section, at www.edn.com/100715pulsea.

Add your comments.

For use in R&D, the 6705B mainframe houses a variety of modules, including the 6781A and B SMUs, which perform comprehensive tests on battery-powered products and system components.

#### NI advances IEEE 802.11n WLAN test

ational Instruments has introduced Version 2.0 of its WLAN (wireless-localarea-network) software suite for IEEE 802.11n WLAN testing. The suite includes enhanced software tool kits for IEEE 802.11n WLAN-signal generation and analysis. The suite integrates with NI's 6.6-GHz PXIe (Peripheral Component Interconnect Extensions for Instrumentation Express) multichannel RF-signal generators and analyzers to deliver phase-coherent MIMO (multiple-input/multiple-output) RF measurements or IEEE 802.11n WLAN testing. The software also delivers high speed for EVM (error-vector magnitude) and spectrummask measurements.

Suite 2.0 adds IEEE 802.11n support to the generation and analysis tool kits to facilitate MIMO testing with true port-to-port phase coherency. For measurements, the tool kit integrates with NI's 6.6-GHz, two-, three-, and four-channel PXIe-5663E VSAs (vector-signal analyzers) to provide accurate multistream MIMO measurements. For signal generation, the tool kit integrates with NI's 6.6-GHz, two-, three-, and four-channel PXIe-5673E VSGs

The new NI WLAN measurement suite adds a variety of software features to improve measurement performance and ease of use.

(vector-signal generators) to generate true phase-coherent, multistream RF signals.

In addition to 802.11n MIMO support, the latest version of the NI WLAN measurement suite improves on the previous version with faster measurement. When you combine it with the latest NI PXIe-8133 quad-core embedded controller, the system can perform composite EVM and power measurements in 7 msec. A result of the tool kit's multicoreenabled measurement algorithms, the fast measurement is crucial for reducing test times and lowering the costs of testing wireless devices.

The suite also adds a variety of software features to improve

measurement performance and ease of use. Engineers can software-enable its resolution-bandwidth-filter feature to remove broadband noise and increase EVM-measurement accuracy. With front-end filtering, engineers can achieve residual EVM accuracy of better than -47 dB when testing WLAN devices.

The suite includes soft front panels for signal generation and analysis to support a range of WLAN IEEE 802.11n configurations, including 4×4 MIMO, and to report measurement results and traces. In addition, engineers can use the measurement suite as either a standalone executable or an API (application-programming interface) in LabView, in the NI LabWindows/CVI ANSI C environment, or in other C, C++, and .NET development systems.

Prices for the NI WLAN measurement suite for IEEE 802.11a/b/g/n start at \$5999, prices for the NI WLANgeneration tool kit for IEEE 802.11a/b/g/ start at \$3999, and prices for the WLANanalysis tool kit for IEEE 802.11a/b/g/n start at \$3999.

—by Rick Nelson

▶National Instruments,

www.ni.com.

#### IP BLOCK MAKES AUDIO-BANDWIDTH 12-BIT ADC FROM DIGITAL LOGIC

Targeting applications in FPGAs and ASICs, Stellamar has created an IP (intellectual-property) block that uses digital circuitry to make a highquality ADC. The scheme uses an LVDS (low-voltage-differential-signaling) input as a comparator. By adding a few passive components to the block, you can achieve 12-bit accuracy over a bandwidth of 15 kHz. At 15- and 4-kHz bandwidths, SNRs (signal-to-noise ratios) are 68 and 72 dB, respectively. The design exhibits no missing codes.

One pin of the LVDS pair serves as a singleended analog input; the other is a feedback pin for the IP block. You can use two of these blocks for a differential input. The analog-input range can sweep through the entire common-mode range of the I/O circuitry, or you can design it to run over a narrower range of voltages with a specified common-mode voltage. The design also works in military applications; you can build it in radiationhardened CMOS or SOI (silicon-on-insulator). The company will sell the IP block for a fixed NRE (nonrecurring-engineering) fee, plus a per-unit royalty. Stellamar demonstrates the design's operation in many FPGAs. -by Paul Rako

Stellamar, www. stellamar.com.

#### Dilbert By Scott Adams

#### Low-power e-nose checks air quality

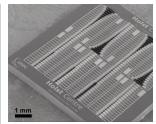

MEC (Interuniversity Microelectronics Centre) and the Holst Centre have developed sensitive integrated sensing elements for gas detection in the form of high-density arrays of polymer-coated microbridges within a MEMS (microelectromechanical-system) device. The device can detect parts-per-million-level concentrations of vapors using on-chip-integrated read-out techniques. The demonstrated technology is suitable for miniaturization of electronic-nose devices. thanks to its small form factor and power consumption of less than 1 µW/bridge.

Microbridge arrays within a MEMS device constitute an e-nose. A polymer specific to a particular gas coats each microbridge.

Mercedes Crego-Calama, principal researcher at Holst Centre/IMEC and program director for Holst Centre's Human++ program, says that each MEMS bridge within an e-nose device acquires extra mass in the presence of volatile chemical vapors, changing its piezoelectric characteristics. Arrays of such MEMS bridges, she says, can resolve and identify multiple chemical contaminants in an environment and help warn allergy or asthma suffers to avoid potentially harmful environments.

The MEMS-bridge architecture operates at lower power than alternative cantileverbased approaches. Crego-Calama also describes a low-cost manufacturing approach, in which commercial ink-jet-printing technology can deposit the polymers sensitive to specific chemical vapors onto the MEMS structures. The e-nose

can monitor air quality, identify pathogens, monitor food ripeness or spoilage, monitor physiological conditions—from breath analysis, for example—and detect biological or chemical weapons.

Within an e-nose device, suspended structures vibrate individually, and changes in their modes of vibration, or resonances, indicate the absorption of a vapor as each bridge device's unique polymer coating determines. Work is ongoing to integrate the structures with low-power analog readout circuits and to demonstrate simultaneous measurements from multiple structures.

-by Rick Nelson

**►IMEC**, www.imec.be.

**⊳**Holst Centre.

www.holstcentre.com.

#### TOOL GIVES EARLY AREA, POWER, AND TIMING ESTIMATES

Atrenta has announced the SpyGlass-Physical software tool, which enables RTL (register-transfer-level) engineers to achieve faster design closure by modeling physical-implementation effects at the RTL stage of the design. Previous members of the SpyGlass family provide information on whether a design is syntactically correct and testable; the new member provides early estimates of area, power, timing, and routability for RTL designers who lack physical-design expertise or tools.

According to Ravi Varadarajan, Atrenta fellow, the new tool does not replace a customer's favorite implementation tools but rather makes them more efficient, allowing designers to identify problems earlier in the design cycle.

In addition, the time penalties of successive iterations using traditional tools—in which you find problems after place and route, for instance—limit the amount of exploration designers can do, with the result that they might settle for a suboptimal solution. SpyGlass-Physical alleviates that problem.

François Rémond, director of CAD at STMicroelectronics (www.st.com), describes his use of the SpyGlass-Physical tool in the design of a 55-nm set-topbox chip, which includes 209 million transistors, 230 clocks, 7 million placed instances, 500 signal pads, 53 RTL-IP (intellectual-property) blocks, and 160 hard-IP blocks. He explains that the timing and physical closure of such chips represent a big challenge. "We needed a tool that would partition our SOCs [systems on chips] based on our requirements and provide trade-off analysis and guidance for our implementation tools," Rémond says. "The SpyGlass-Physical product achieved that [goal] on 40- and 32-nm SOCs in significantly shorter time than we expected."

SpyGlass-Physical runtimes can range from two to three hours, which represents a large savings over finding problems deep in the implementation. The product helps to achieve performance targets in concurrent block- and SOC-development processes by using a set of interactive implementation-analysis features.

The result is enhanced guidance for the implementation of both IP blocks and full-chip SOCs. SpyGlass users can easily integrate the product into their design flows and realize the benefits of early physical-implementation modeling.

"Chip-design companies have a great need to reach faster design closure than ... current flows [support]," says Ajoy Bose, PhD, chairman, president, and chief executive officer of Atrenta. "The ability to model the impact of physical implementation on the design at an early stage is a critical aspect that is missing from to-day's RTL flows."

The SpyGlass-Physical product addresses this gap by providing early estimates of area, power, timing, and routing congestion.—by Rick Nelson

Atrenta, www.atrenta.com.

## Open-source development board: \$4.30

pen-source hardware appeals most strongly to developers who want or need to access all parts of their hardware and software platform. To address that requirement, Texas Instruments' new Launchpad development board puts a fully realized 16-bit microcontroller platform within the grasp of any designer for \$4.30.

The platform employs TI's Value Line family of low-cost, 16-bit microcontrollers and comes with the 14-pin Value Line

The \$4.30, open-source Launchpad development board puts a 16-bit micro-controller platform, including a 10-bit ADC, comparators, and an internal temperature sensor, within the grasp of any designer.

MSP430G2211 and MSP430G2231 processors. Demo firmware on one preprogrammed processor demonstrates the use of on-chip peripherals. You can swap the processors out in the on-board 20-pin DIP socket as needed. An integrated, USB-powered emulator permits flash programming, firmware debugging, and serial communication. It can also serve as a programmer or a debugger for any microcontroller in the MSP430 family. TI offers the free, downloadable Code Composer Studio and IAR Embedded Workbench KickStart compiler/debugger software packages.

—by Margery Conner ▶Texas Instruments, www.ti.com.

You Tube

## Equivalent-time-sampling scope improves accuracy of characterizing high-speed designs

gilent Technologies has expanded its DCA (digital-communications-analyzer) portfolio with the introduction of the 86100D DCA-X (extended) wide-bandwidth equivalenttime-sampling oscilloscope. The instrument provides the tools you need to easily and accurately characterize highspeed digital designs. The DCA-X mainframe platform lets you make next-generation measurements that include integrated de-embedding. The unit is backward-compatible with all previous DCA models and is fully codecompatible with the 86100C mainframe. Future models will support 16 channels, which will enable you to efficiently test parallel designs and will achieve higher throughput in manufacturing.

The DCA series' high analog bandwidth, low noise, and low measurement jitter help you to see the true performance of your designs on signals whose data rates range from 50 Mbps

to more than 40 Gbps. You can configure the modular DCA platform for optical, electrical, TDR/TDT (time-domain-reflectometry/time-domain-transmission), and S (scattering)-parameter measurements. The DCA-X improves on the accuracy and ease of use of the 86100C DCA-J (jitter) by integrating de-embedding and embedding using the 86100D-Sim InfiniiSim-DCA software license

Usability enhancements include graphical-signal processing and dual user interfaces—the FlexDCA, a new, customizable, vector-based interface for scope, eye, and jitter measurements, and the DCA-J. The device also features as many as 64 simultaneous measurements and data-dependent pulse-width-shrinkage, uncorrelated-jitter, and pre- and deemphasis measurements.

Hardware enhancements include vertical-gain and offset controls for all channels and functions, a userdefined multipurpose button, a user-defined analog-control knob, a faster CPU, and support for as many as 16 measurement channels.

As data rates increase, fixtures and probes play a larger role in degrading waveform fidelity and reducing measurement margins. During verification or compliance testing, you must often remove these unwanted effects to see your devices' true performance. It is common to measure a clean transmitter output and to simulate this signal at the output of a typical channel-loss model. The 86100D-Sim InfiniiSim-DCA waveform-transformation tool set, a new 86100D software option, allows you to quickly and accurately perform both of these tasks.

Agilent has also upgraded its N101A FlexDCA remote-access software so that it now supports both the 86100C DCA-J and the 86100D DCA-X mainframes. The N1010A, a PC-based version of the DCA-X user interface, extends control of the scope through a LAN to a remote lab or home-office PC and allows you to analyze waveforms offline.

US prices for the 86100D DCA-X start at \$21,500. US prices for the 86100D-Sim InfiniiSim-DCA waveform-transformation software start at \$5000.

-by Dan Strassberg▶Agilent Technologies,www.agilent.com.

The 86100D DCA-X equivalent-time-sampling-scope main-frame, which can acquire signals at frequencies as high as 90 GHz, accepts all of the plug-in modules that its predecessors accept. It also accepts new plug-ins that significantly expand its measurement capabilities and lets you choose between two user interfaces.

#### Seagate takes cautious approach to solid-state drives

eagate's new operating-system-agnostic Momentus XT solid-state drives present themselves as conventional 3-Gbps SATA (serial-advanced-technology-attachment) hard drives. Magnetic-media capacities are larger than those of the company's previous offer-

ings, befitting the latest PMR (perpendicular-magnetic-recording) areal density capabilities. Flash-memory capacity is 4 Gbytes, and RAM buffers hold 32 Mbytes. The magnetic media's rotational speed is 7200 rpm, versus 5400 rpm in the first-generation approach.

Seagate claims that Mo-

mentus XT prices will track those of conventional hard drives to within a capacity-dependent \$50 to \$90 markup. Prices for 500-, 320-, and 250-Gbyte units are \$156, \$122, and \$113, respectively.

The drives use SLC (single-level-cell) NAND-flash memory, which is more expensive and more reliable than MLC (multi-

level-cell) memory, dispensing with the need for wear-leveling, error-detection and -correction, and erase-block-retirement media-management algorithms. System writes bypass flash memory, so performance limitations don't hamper them. Compare prices on 250- to 500-Gbyte solid-state drives, and the price advantage of Momentus XT will soon become evident. —by Brian Dipert

**Seagate Technology**, www.seagate.com.

## Analog Devices: enabling the designs that make a difference in people's lives.

ADI's family of innovative smart meter solutions offers greater control, communication, and monitoring capabilities.

Measurement, processing, and communications solutions for intelligent energy systems. Optimizing the supply and demand for electricity is a goal we all share. At ADI, we provide data converter, amplifier, processor, and wired and wireless communications technologies to create leading-edge solutions for today's energy market. Our products give consumers precise, real-time smart meter information, enabling them to reduce energy consumption; utilities the ability to accurately monitor grid conditions, increasing system efficiency; and energy producers the ability to optimize solar and wind power generation, reducing fossil fuel dependence. For over 40 years, ADI has brought innovation and imagination to critical designs, including those that make our energy-sensitive world a better place. Learn more at <a href="https://www.analog.com/energy">www.analog.com/energy</a>.

#### BY HOWARD JOHNSON, PhD

#### Water analogy

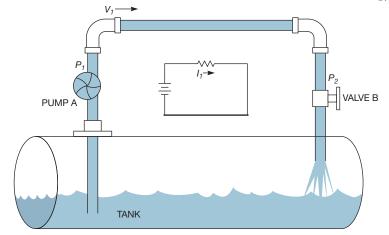

ump A in Figure 1 forces water at constant pressure,  $P_1$ , around a closed loop. As long as Valve B remains open or at least partially open, the water flowing in the pipe attains steady velocity,  $V_1$ . The pump pressure; the viscosity of water; and the effective fluid-flow resistance of the pipes, valves, and elbows used in the circuit determine this velocity. The plumbing circuit is analogous to a simple electrical circuit comprising a battery, a resistor, and a connection from the opposite end of the resistor back to the battery, representing the tank. The electrostatic pressure the battery creates corresponds to water pressure at the head of the pump. The circulation of electrical current in the wires corresponds to the circulation of water in the plumbing.

The concept of resistance translates easily between the two circuits. If you define the fluid-flow resistance of a pipe as the pressure difference from end to end divided by its flow, then a long, skinny pipe makes a high resistance. A big, fat pipe, such as the one still gushing oil into the Gulf of Mexico, makes a low resistance. This fluid-flow equivalence works so naturally that most students, years later at the end of their careers, still think of a

high resistance as a long, skinny pipe.

One major difference between the movement of water and that of electrons concerns linearity. The fluid-flow resistance of a piece of pipe varies almost quadratically with the flow, as opposed to the exquisitely linear relationship you normally expect when working with an electrical resistance. Nobody brought that fact to my attention when we discussed the water-flow analogy in

Figure 1 Water circulates endlessly around this closed loop, much like electrical current.

school, but, if you want to properly size your lawn-sprinkler system's pipes, you'd better check it out.

The lack of linearity in water-flow systems works to the advantage of a student's understanding. It focuses attention on two fundamental principles of circuit analysis. First, you must always maintain the correct relation of pressure drop to flow for every device throughout a circuit. Second, no water enters or exits a closed system. Those two rules are sufficient to develop a rich understanding of circuit behavior.

On the other hand, the simple linear nature of electronic components tempts electrical engineers to attack every problem with linear matrix analysis and Laplace transforms. These powerful tools confuse beginners. Rather than begin with linear analysis, every electrical-engineering student should first complete a thorough study of nonlinear circuits. Devices such as FETs and bipolar transistors are nonlinear and temperature-dependent anyway, so it makes sense to first introduce nonlinear behavior.

Water- and electron-based circuits, both ultimately dependent on the movement of myriad tiny particles, share many similarities beyond simple pressure and flow relations. For example, if you force too much water through a pipe, the required rise in pressure may burst the pipe, after which nothing flows through to the end and you have to mop up a huge mess. In an electrical circuit, an overtaxed resistor overheats and melts, after which no current flows and you must deal with the smell.

At the other end of the signal-amplitude scale, Brownian motion affects sensitive hydraulic systems, such as the diffusion of ions throughout a nerve ending. Thermal noise affects electrical circuits. It's the same effect either way. We are all just pushing particles around closed loops.EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Email him at howie03@sigcon.com.

## NOTES

#### Fast Time Division Duplex (TDD) Transmission Using an Upconverting Mixer with a High Side Switch - Design Note 480

Vladimir Dvorkin

#### Introduction

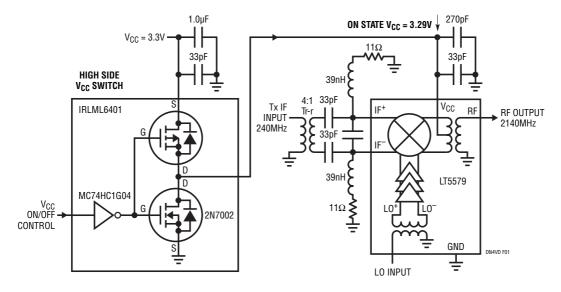

Many wireless infrastructure time division duplex (TDD) transmit applications require fast on/off switching of the transmitter, typically within one to five microseconds. There are several different ways to implement fast Tx on/off switching, including the use of RF switches in the signal path, or on/off switching of the supply voltage for different stages of the transmitter chain. The advantages of the latter method are low cost, very good performance and power saving during the Tx off-time. In particular, a good place to apply supply switching is at the transmit upconverting mixer because this removes both the transmit signal and all other mixing products from the mixer RF output.

The LT®5579 high performance upconverting mixer fits various TDD and Burst Mode® transmitter applications with output frequencies up to 3.8GHz. Fast on/off supply voltage (V<sub>CC</sub>) switching for the LT5579 is as simple as adding an external high side power supply switch (note that this technique is equally effective for the lower frequency upconverting mixer, LT5578).

#### High Side V<sub>CC</sub> Switch for a Burst Mode Transmitter Using the LT5579 Mixer

The high side V<sub>CC</sub> switch circuit in Figure 1 uses a P-channel MOSFET (IRLML6401) with an R<sub>DS(ON)</sub> of less than 0.1Ω. An N-channel enhancement mode FÉT (2N7002). connected from the drain of IRLML6401 to ground, further improves fall time. The 2N7002's  $R_{DS(0N)}$  is less than  $4\Omega$ , which is sufficient for this application.

The input driver for the high side  $V_{CC}$  switch is a high speed CMOS inverter (MC74HC1G04) capable of driving capacitive loads. The IRLML6401 input capacitance is typically 830pF and the 2N7002 input capacitance is

LT, LTC, LTM, Burst Mode, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners

Figure 1. Upconverting Mixer with High Side V<sub>CC</sub> Switch

under 50pF. For faster rise times, two high speed CMOS drivers can be used in parallel. Likewise, for faster fall times, a different N-channel MOSFET with lower on-resistance can be used.

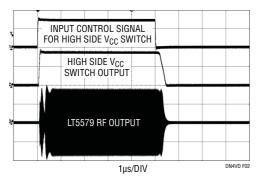

With the LT5579 supply current of 220mA, the power supply voltage drop across the MOSFET is only 11mV. The response time of the high side  $V_{\rm CC}$  switch is shown in Figure 2. Total turn-on time is only 650ns and total turn-off time is 500ns. These measurements were performed using two RF bypass capacitors at the mixer  $V_{\rm CC}$  pin (33pF and 270pF). Higher value RF bypass capacitors can be used, which would result in correspondingly slower rise/fall times.

Figure 2. V<sub>CC</sub> Turn-On and Turn-Off Waveforms

The LT5579 upconverting mixer circuit shown in Figure 1 was optimized and tested at an RF output frequency of 2140MHz. The RF output envelope in Figure 2 shows a dip about 300ns after the  $V_{CC}$  switch turns on, followed by another, smaller dip at about the 500ns point. Both dips represent the mixer's internal feedback circuit reaction to the ramping supply voltage.

LO leakage to the RF output of the LT5579 was measured at -40 dBm when  $V_{CC}$  is on and -46 dBm for  $V_{CC}$  off. The LO port of the LT5579 is internally matched and has a return loss of 10dB to 18dB over a frequency range of 1100MHz to 3200MHz.

When the LT5579 mixer is in the off state, the return loss of the LO port is about 3dB to 5dB across the same frequency range of 1100MHz to 3200MHz. It is advisable to use an LO injection VCO with a buffered output for better reverse isolation, and to avoid any VCO pulling while the LO port impedance changes when switching between the on and off states.

#### Conclusion

LT5579 and LT5578 mixers without an ENABLE pin can be used in TDD applications with external  $V_{CC}$  switching. Using only three parts (IRLML6401, 2N7002 and an MC74HC1G04), a high performance high side  $V_{CC}$  switch allows turn-on and turn-off in under 1 $\mu$ s.

Data Sheet Download

www.linear.com

For applications help, call (408) 432-1900, Ext. 3866

# ESL SYNTHESIS: TIPS FOR IMPLEMENTING A VIABLE ESL-SYNTHESIS FLOW BY NANCY WU, GARY SMITH EDA HERE'S A CHECKLIST OF WHAT TO DO AND WHAT NOT TO DO WHEN PERFORMING ESL SYNTHESIS. THE ITEMS DISCUSSED HELP SET REALISTIC EXPECTATIONS FOR THOSE ABOUT TO TAKE THE PLUNGE.

t would be an understatement to suggest that the ESL (electronic-system-level) market is an enigma. At the 1994 DAC (Design Automation Conference), vendors touted ESL as the panacea that would catapult the next growth spurt in the EDA market. The next 10 to 12 years were a bit disappointing in regard to the mainstream adoption of ESL methods. Depending on how you break up the data, the ESL market in 2005 likely accounted for \$150 million in revenues across approximately 20 to 25 companies. Thus, mid-2006 represents a good point at which to assess the ESL user community.

According to early adopters at the time, the top three benefits of ESL were its ability for high-level specification, its strong capabilities for architectural exploration, and the existence of reasonable tools and methods for high-level verification. During the same period, the top three challenges were the fact that ESL offered no clear path to RTL (register-transfer-level) implementation from high-level specification, significant gaps in ESL methodology and flow, and the absence of embedded-software designers from system-level interactions. According to an anonymous user at a major North American electronics-system OEM at the time, the Holy Grail for ESL was an executable and synthesizable specification that designers can simulate and eventually sign off at a high level of abstraction.

By mid-2009, this Holy Grail was still missing. But there has been progress, especially in the synthesizable-specification arena. EDA analyst Gary Smith says that three key segments in ESL are stable and

growing: architectural design and exploration, which is primarily the behavioral exploration segment that CoWare and The MathWorks serve; software virtual prototypes, or virtual software development, the tools—from CoWare, Synopsys, Vast, and other vendors—that enable software validation on models of the intended hardware; and ESL synthesis, the tools that generate RTL code from various high-level specifications, including C/C++, and SystemC from companies including Forte, Mentor, and Synfora. Smith calculates that each of these segments grew 30 to 80% on a year-overyear basis during 2008.

As with any other technology, ESL invites squabbling among vendor technologists and early adopters about the goal of synthesis. One goal seems to capture the key aspects from a user perspective: An ESL-synthesis platform enables highlevel specification, optimization, and verification and automatically leads to verifiable RTL code with result quality

comparable to that of manual methods.

Smith asserts that a viable path to implementation from high-level specification to RTL code enables mainstream users to adopt leading ESL-synthesis tools. In his view, the time for return-on-investment justification has passed; it is now time to educate new adopters about rules of deploying ESL-synthesis tools.

Desaisive Technology Research takes a realistic approach toward measuring and forecasting the ESL market. Table 1 compares the emerging ESL market with the more traditional RTL market. A migration in revenues from RTL to ESL design is expected during the next three to five years. RTL will not disappear anytime soon. However, the ESL segment should continue to outpace the overall EDA market, and the RTL-design and -verification revenues will likely prove to have peaked in 2007.

Based on input from the technical media and user postings over the past six months, there still appears to be a fervent, vendor-biased debate on one key issue: which high-level language should participants in the EDL market use? This issue is not trivial; it lies at the core of industry participants' objectives for deploying an ESL-synthesis flow.

The choice of high-level language can be a critical factor for successful use of ESL. C/C++ offers the highest level of algorithmic exploration, and designers can easily simulate it with freeware. The greatest challenge is that C/C++

has sequential execution semantics and provides no explicit support for parallel structures. Obtaining good results for the synthesized RTL requires an advanced parallelizing compiler embedded in the synthesis tool to automatically extract parallelism in an application. Thus, the quality of the parallelizing compiler distinguishes one tool from another.

SystemC has emerged as the high-level specification language for hardware modeling and verification. SystemC has seen strong adoption on the hardware specification and, therefore, verification, side in Asia—primarily Japan—and Europe and within a host of consumerelectronics OEMs. SystemVerilog, on

AT A GLANCE

- High-level synthesis is finally a factor in SOC (system-on-chip) design.

- Dialects of C predominate.

- Both design and verification should move to the highest level of abstraction.

- Applying high-level tools to the entire design produces the best gains.

the other hand, is essentially a high-level hardware-verification language, one step higher than RTL. Clearly, the benefits a user hopes to derive from adopting ESL drive the choice of high-level language and, thus, the level of abstraction.

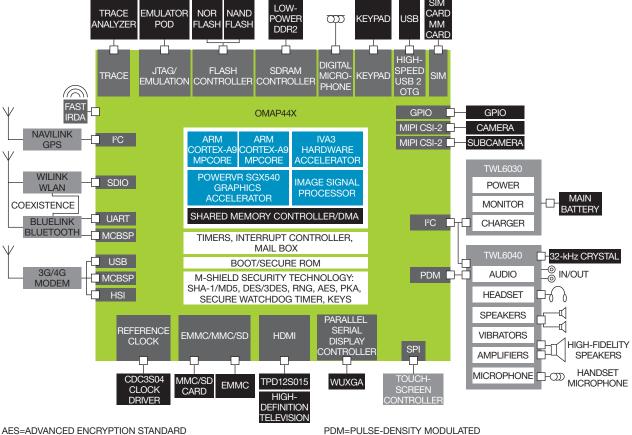

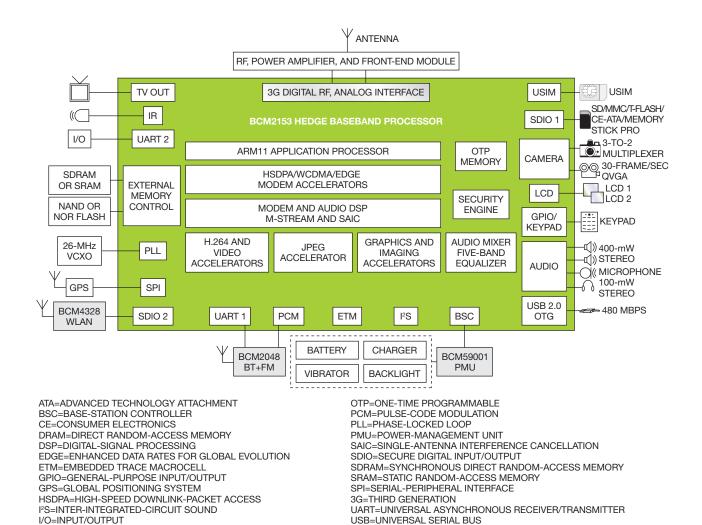

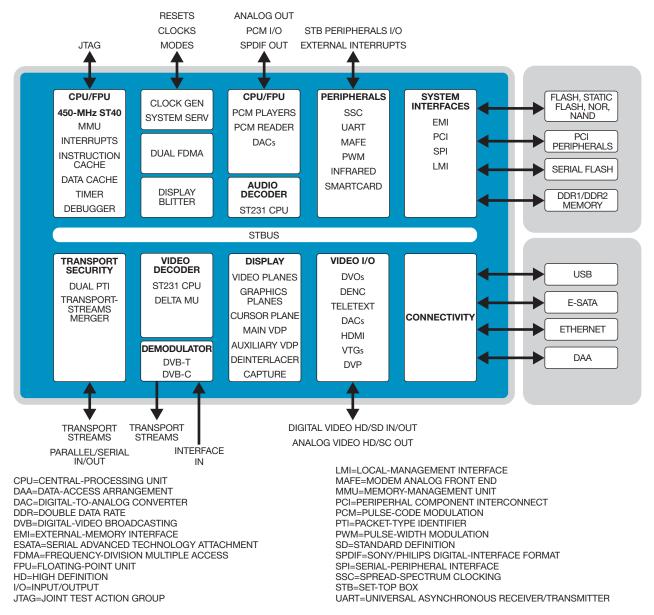

An examination of some state-of-theart SOC (system-on-chip) architectures may help ascertain the nature and complexity of the challenges facing these design teams. Specifically, consider Texas Instruments' OMAP (Open Multimedia Application Platform) 4 processor, an ARM-based baseband processor for advanced cell phones (Figure 1); Broadcom's BCM2153 processor, an ARMbased baseband processor for multimedia applications (Figure 2); and STMicroelectronics' STi7167 decoder (Figure 3), an advanced set-top box-decoder employing the ST40 CPU/FPU (floatingpoint unit).

DES=DATA ENCRYPTION STANDARD DRAM=DIRECT RANDOM-ACCESS MEMORY EMMC=EMBEDDED MULTIMEDIA CARD 4G=FOURTH GENERATION GPIO=GENERAL-PURPOSE INPUT/OUTPUT HDMI=HIGH-DEFINITION MULTIMEDIA INTERFACE HSI=HIGH-SPEED INTERFACE I2C=INTER-INTEGRATED CIRCUIT JTAG=JOINT TEST ACTION GROUP MCBSP=MULTICHANNEL BUFFERED SERIAL PORT MD5=MESSAGE DIGEST 5 MIPI=MUSIC INDUSTRY PROCESSOR INTERFACE MM=MULTIMEDIA MMC=MUITIMEDIA CARD OTG=ON-THE-GO

PDM=PULSE-DENSITY MODULATED PKA=PUBLIC-KEY ALGORITHM RNG=RANDOM-NUMBER GENERATOR ROM=READ-ONLY MEMORY SD=SECURE DIGITAL SDIO=SECURE DIGITAL INPUT/OUTPUT SDRAM=SYNCHRONOUS DIRECT RANDOM-ACCESS MEMORY SHA=SECURE HASH ALGORITHM SIM=SUBSCRIBER-IDENTITY MODULE SPI=SERIAL-PERIPHERAL INTERFACE 3DES=TRIPLE DATA ENCRYPTION STANDARD 3G=THIRD GENERATION UART=UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER WLAN=WIRELESS LOCAL-AREA NETWORK

USB=UNIVERSAL SERIAL BUS

Figure 1 TI's OMPA-9 architecture clusters two ARM Cortex A9 processors with key accelerators.

| TABLE 1 EDA SEGMENTS REVENUE ANALYSIS (\$ MILLIONS)    |        |        |        |       |       |           |

|--------------------------------------------------------|--------|--------|--------|-------|-------|-----------|

|                                                        | 2006   | 2007   | 2008A  | 2009E | 2010E | 5-Yr CAGR |

| High-level design and verification (ESL)               | 121.6  | 139.5  | 159.5  | 180   | 205   |           |

| Year-over-year growth                                  | 16%    | 15%    | 14%    | 13%   | 14%   | 14%       |

| Percentage of total computer-aided engineering segment | 5%     | 6%     | 7%     | 8%    | 9%    |           |

| RTL design and verification (traditional)              | 651.2  | 696.9  | 634.6  | 625   | 625   |           |

| Year-over-year growth                                  | 7%     | 7%     | -9%    | -2%   | 0%    | 1%        |

| Percentage of total computer-aided engineering segment | 29%    | 28%    | 29%    | 28%   | 28%   |           |

| Total computer-aided-engineering segment               |        | 2467   | 2199.7 | 2200  | 2250  |           |

| Year-over-year growth                                  | 14%    | 11%    | -11%   | 0%    | 2%    | 3%        |

| Total EDA market                                       | 4078.3 | 4464.8 | 3853.7 | 3850  | 3960  |           |

| Year-over-year growth                                  | 14%    | 9%     | -14%   | 0%    | 3%    | 2%        |

Source: EDAC MSS Statistics Report and Desaisive Technology Research analysis

All of these architectures have one or two core processors that assume a supervisory role, a main bus structure, embedded memory, and a variety of off-the-shelf IP (intellectual property) for interfacing and control. Each has three to eight application processors or computationally intensive accelerators. These components include hardware accelerators, graphics accelerators, image-signal processors, video accelerators, and security engines. The application processors and accelerators therefore form, in conjunction with the

interconnection fabric and embeddedsoftware stack, the basis for competitive differentiation of the SOC. Everything else is essentially off-the-shelf IP.

Such application processors and accelerators, along with interblock communications, dictate what you must specify, verify, and synthesize at ESL. The other leg of system-level differentiation comes from the various stacks of application-specific embedded software. Not surprisingly, programmers debug most such software in C/C++ during the architec-

tural and functional-exploration stage. Thus, true ESL-design specification should begin at the C/C++ level. Proponents of SystemC may disagree with this assessment. However, SystemC primarily finds use in transaction-level modeling that enables performance validation at the system level.

The issue of sequential execution of C/C++ and the challenge of handling parallelism and implicit control also arise. Vendors and leading-edge customers offer several observations.

24th International Trade Fair New Munich Trade Fair Centre 09–12 November 2010

#### Time for electronics. Time for the future.

Key topics, trends and technologies. The latest components, systems and applications. Visit electronica 2010, the international trade fair that will show you today what is important tomorrow and generate momentum for real growth.

Parallel event: hybridica. Trade fair for hybrid-component production. www.hybridica.de get the whole picture

www.electronica.de/en

Figure 2 Broadcom's Hedge baseband processor is a single-CPU SOC with a cluster of accelerators.

Most customized logic for new SOCs comprises application processors and accelerators—computationally intensive accelerators with a predominant datapath structure. These architectures put design teams at the forefront of architectural exploration. Architects have for several years been using C/C++ for high-level modeling and specification. The ability to do both high-level specification and functional verification, with an automated path to implementation, brings out the ultimate benefit of adopting ESL. In addition, both Mentor and Synfora have now generated dozens of customers that are willing references that these tools more than adequately handle a flow to RTL. For example, Synfor a boasts a unique parallelizing compiler that seamlessly handles both the datapath and the control-logic components of application accelerators.

IR=INFRARED

OTG=ON-THE-GO

JTAG=JOINT TEST ACTION GROUP LCD=LIQUID-CRYSTAL DISPLAY

You must separate the issues of timing verification and performance verification. The focus of high-level verification is functional behavior and the possibility of running more test vectors. Although C/C++ lacks explicit timing information, designers can specify clock frequency and overall performance requirements and can verify them starting with a high-level specification in C/C++. The design team should, however, relegate the issue of detailed timing analysis to SystemC and RTL.

If the goal of adopting an ESL methodology is to begin with the highest level of abstraction with a proven path to implementation, it makes sense to begin at the C/C++ level. Designers can now generate both an RTL model and a SystemC transaction-level model from this specification. You can successfully implement an ESL synthesis flow using C/

C++, including Mentor's CatapultC and Synfora's Pico. For the more than 75% of the design community still using hand-crafted RTL for design specification and verification, the issue is to outline the options available and set the right set of expectations for successful implementation of an ESL methodology.

USIM=UNIVERAL MOBILE TELECOMMUNICATIONS SYSTEM

WCDMA=WIDEBAND CODE-DIVISION MULTIPLE ACCESS

SUBSCRIBER-IDENTITY MODULE

WLAN=WIRELESS LOCAL-AREA NETWORK

Mentor and Synfora provide a list of top dos and don'ts that their users have adopted after going through the learning curve of implementing an ESL-synthesis flow. Some common themes advise designers to design at the highest level of abstraction; build architecture awareness into the code at the highest possible level of abstraction; and optimize architecture, system, and power constraints at the high-level design phase. Results matter, and the length of the learning curve and ease of adoption are important productivity considerations. However, you cannot

Figure 3 This STMicro set-top box is a single-CPU, multiple-accelerator architecture, but the vendor is vague about the bus architecture.

compromise by accepting results that are not in the same quality range as handcrafted RTL. Keep in mind that these are company- and application-specific metrics that are difficult to generalize.

Consider verification early and often and how it fits into the overall picture of your high-level-synthesis flow. A key benefit of high-level synthesis is to do most of the verification and debugging at the highest level of abstraction. The vendor's ESL-synthesis tool must thus provide capabilities to debug both functional and performance issues rather than force you to debug at RTL. You should also determine whether the ESL tool generates both RTL and SystemC models, so that hardware designers can perform transac-

tion-level-modeling analysis.

Target larger blocks of logic. Otherwise, you derive no productivity benefits, and the flow and methodology will not scale to larger blocks or real-life designs. You should also use true hierarchical abstraction and ensure that the ESL-synthesis tool supports a multilevel hierarchical method. If the tool internally flattens the design before synthesis, this flattening adversely affects your ability to reuse or retune the design. This loss also affects the issue of results.

Your tools should also provide visibility into what you are building and the downstream design implications. You should have high-level control over architectural trade-offs and the ability to

drive RTL implementation.

Systems comprise datapaths, control logic, and IP. The productivity boost of designing at a high level comes from the deployment of complex systems. Pay close attention to how the ESL-synthesis tool handles and optimizes control logic. The synthesis tool should be able to automatically connect the sub-blocks without manual intervention at the RTL.EDN

#### **AUTHOR'S BIOGRAPHY**

Nancy Wu is chief analyst at Gary Smith EDA. She has a master's degree in economics from the University of Michigan—Ann Arbor and a bachelor's degree in economics from the National Taiwan University.

## EM SIMULATION FOR EMC: KEEPING A LID ON INTERFERENCE

FIELD-SOLVER SIMULATION CAN DO YOUR WORK, BUT YOU HAVE TO DO THE THINKING.

BY PAUL RAKO • TECHNICAL EDITOR

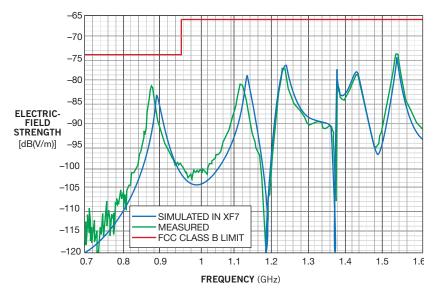

imulating your product's EM (electromagnetic) radiation will help ensure that you pass FCC (Federal Communications Commission) and CE (Conformité Européenne) tests and will keep your project on schedule. Every product must have EMC (electromagnetic-compatibility) tests. The FCC requires that you test your products to ensure that EM radiation will not cause interference with radios, phones, and TVs. In addition to testing for EM radiation, your product must also exhibit electromagnetic immunity, meaning that a strike from a defined EM pulse will not significantly disturb the product's performance (Reference 1).

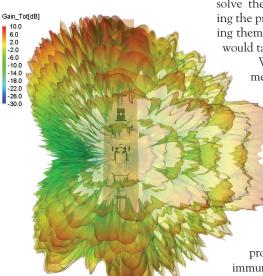

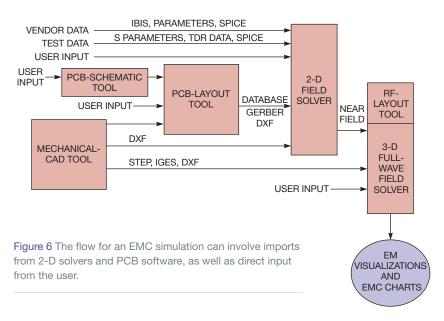

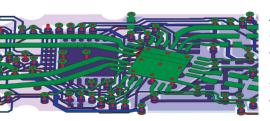

You need sophisticated software tools to perform EM simulations. These simulations must take into account both small and large features over a broad frequency range (Figure 1). You must also select an appropriate simulation method, which can be either a time-domain technique, such as FEM (finite-element method), or a frequency-based one, such as MOM (method of moments). For the largest problems, you need to break the simulations into subdomains or use asymptotic-solutions techniques.

Once you have a powerful computer and the right software, you must place physical and electrical data into the software using database importation or by feeding in mechanical configurations with Gerber and DXF (Draw-

ing Exchange Format) files and manually entering dielectric constants and board-stackup specifications. Finally, you must provide a stimulus to the software, either with Spice or S-parameter data or with a near-field-simulation result from a previous simulation on a subsystem in the product.

#### **SPICE VERSUS FIELD SOLVER**

You cannot use Spice to simulate EMC because Spice is a matrix-math computational solver for Kirchhoff's equations that uses lumped-element models of discrete components. At best, you can use Spice to model a lossy transmission line to define what happens to the signal, but it does not reveal which fields radiate into space. For this problem, you need a field-solver simula-

tion (Reference 2). A field solver uses finite elements, meshing, and iteration to solve Maxwell's equations for your circuit design. EM-simulation software must account for the mechanical configuration and the materials you use in the design (see sidebar "Computer power").

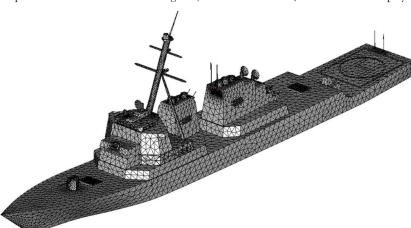

The highest frequencies you are trying to simulate and the size of the circuit dictate the scope of the field-solver problems you will encounter. Wavelengths are 30m at 10 MHz, meaning that a 1-cm trace is much smaller than the wavelength (**Figure 2**). The software would not have to mesh the trace into smaller sections to iterate toward a solution. The 30m wave acts almost uniformly on the 1-cm trace.

Imagine a 10-GHz radar signal with a 2-cm wavelength bouncing off a battle-ship. The field-solver software must

Figure 1 The EM pattern from a small antenna on a large ship exhibits the multiscale problem of an EM simulation (courtesy Feko).

break the battleship into billions of tiny meshes, fitting 10 or even 100 into each square centimeter of the ship's surface. The surface of a metal battleship is not purely reflective, so the software must do 3-D meshing and has even more elements to compute because it must also do the interior areas. The workstation that runs the software needs hundreds of gigabytes of memory to store intermediate calculations for the meshes, and it would take months to solve for

#### AT A GLANCE

- ➤ EM (electromagnetic) simulation requires the use of powerful computers.

- ➤ Time- and frequency-domain techniques both find use in EM simulation.

- ➤ To perform EM simulation, you must import physical configurations and materials.

- Simulation requires multiple iterations and techniques.

- ≥ EM simulation beats guessing about EMC (electromagnetic compatibility).

- Simulation is nonintuitive.

the fields over this large area. You can solve the memory problem by breaking the problem into domains and solving them iteratively, but that approach would take even longer.

When you test for EMC, small mechanical features result in big

changes in performance. A slot in a cover, a misrouted trace, or an aluminum heat sink on an IC package can all cause your product to fail EMC-radiation testing. These mechanical features serve as antennas, so they also receive energy from their

surroundings, giving your

product poor electromagnetic immunity. The standards require compliance to frequencies of 960 MHz and beyond. For this reason, simulating for EMC is a broadband problem with heavy computational requirements. You must simulate for those frequencies; thus, simulating a large system takes an unacceptably long time. The

complexity of the problem is monstrous even for a rather simple product. Also, multiple phenomena, including electrical fields radiating from traces, magnetic fields from inductors, and both types of fields radiating into and from cables, are responsible for EMI (electromagnetic interference).

A typical EM-simulation strategy divides the problem into pieces and depends on both relative and absolute measurements. You need to know how customers will use the product, divide your EMC analysis into manageable pieces, and then evaluate those pieces as they relate to the whole problem. The principle of superposition can be a big help. It states that, for all linear systems, the net response at a given place and time that two or more stimuli cause is the sum of the responses that each stimulus individually would have caused. If three main contributors are affecting your EMI signature, you can individually simulate each one, with different techniques if necessary, and then add the results in an rms (rootmean-square) fashion if they are not related. Sometimes, though, one system affects the other, and they do interact.

Once you have simulated the PCB (printed-circuit board), you represent that simulation as a radiating model that you then plug into a larger assembly. Even if you can use likely signals to simulate the radiation from your PCB, you may also have a few switching power supplies that have not only electric fields, but also magnetic ones. A case surrounds these components, and the cables from the product are antennas that radiate energy to make you fail EMC testing and receive energy to make your circuit fail immunity tests. You may also have to decide how disparate radiation patterns add up to a total emissions level. That decision may bring up the ugly reality of nonlinear

| TABLE 1 FINITE-ELEMENT AND TIME-DOMAIN TECHNIQUES |                                 |     |    |               |            |  |

|---------------------------------------------------|---------------------------------|-----|----|---------------|------------|--|

| Frequency                                         | Electrical length (wavelengths) | FEM | TD | MOM/<br>MLFMM | Asymptotic |  |

| 1 MHz                                             | 0.5                             | X   | X  | X             |            |  |

| 10 Mz                                             | 5                               | X   | X  | X             |            |  |

| 100 MHz                                           | 50                              |     | Х  | X             |            |  |

| 1 GHz                                             | 500                             |     |    | X             | X          |  |

| 10 GHz                                            | 5000                            |     |    |               | X          |  |

Source: CST

circuits, such as RF-power amplifiers that you drive into saturation to get good efficiency. Superposition techniques don't work in nonlinear systems and may cause you to underestimate the radiation from the circuitry.

#### **SELECTING A TECHNIQUE**

The mathematicians and software wizards who work at field-solver companies have developed many methods to help you do EM simulations. You can use 2-D simulation programs, such as HyperLynx and SIwave (signal-integrity wave) to evaluate the EMC of a PCB. Fixing the signal- or power-integrity problems on the card often fixes your EMC problem, as well. You can use time-domain simulations for lower frequencies and smaller physical problems. The key benefit of the time-domain techniques is that they use GPU (graphics-processing-unit) cards, which speed up the math.

James Stack, training, applications, and consulting manager at Remcom Technology Solutions, reports that adding one GPU speeds solvers by a factor of 30 and stuffing your computer with four GPU cards can speed things up by a factor of 150. David Johns, vice president of technical support and engineering at CST (Computer Simulation Technology), reports that his company's time-domain solver runs problems 12 times faster with a GPU.

Unfortunately, at higher frequencies, time-domain techniques are not the best way to solve for EM fields. FEM and time-domain field-solver techniques work best for slower signals,

**COMPUTER POWER**

As you evaluate software packages to help you with EMC (electromagnetic compatibility), be sure to ascertain which formats the packages import as physical models and which PCB (printed-circuit-board) packages they work with. Ask the vendors how the software represents stimulus functions and make sure that you can create those representations. Finally, buy the proper type of workstation. It should have multiple GPUs (graphics-processing units) if you have the time and the budget for time-domain simulations. If you are doing faster frequency-based solving, then you need multiple cores and multiple CPUs along with a large memory to store the intermediate results as the simulation progresses.

Modern computers can often solve—in hours—complex products, such as computer-sized systems. A key spec is how large a problem the computer can solve overnight—a likely scenario. You spend the day setting up and designing the configuration, and you then launch the field solver before you go home. The next morning, you will be able to look at the solutions and decide on the next iteration of design changes and simulations. Just remember that working on EMC problems is no place for departmental silos. The fixes will be both mechanical and electrical, and the team working on EMC needs the authority to change anything that will solve the problem.

while MOM and asymptotic solvers work for faster speeds and larger problems (Table 1). You are better off using a frequency-based solver in a PC workstation with lots of memory and multiple CPU cores. Companies such as Feko and CST use MLFMM (multilevel-fast-multipole-method) techniques, which solve large problems with less computer power. As the problems become large and must run at frequencies greater than 10 GHz, you must use special solvers that can do asymptotic analysis, which solves for large sets. In some simulations, one physical domain affects another (see sidebar "Multiphys-

ics keeps tabs on your design").

Some products, such as those from Cadence, Mentor Graphics, and Zuken, have tools to get electrical and physical information into the simulation software. When you do your PCB design in these vendors' tools, the vendors provide a complete representation of the PCB-layer stackup and material, allowing their signal-integrity and field-solver tools to use this data in their simulations.

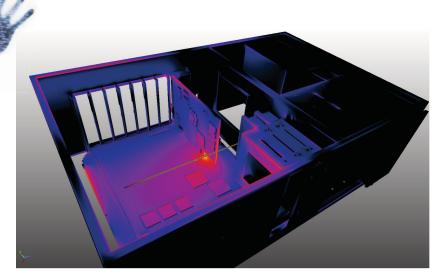

Also make sure that point tools can accept your PCB data. CST and Sigrity take databases from Cadence, Mentor, Zuken, and Altium, and these tools and many others accept ODB (open-database)++ PCB fabrication to define the physical configuration and materials in PCBs. Full-wave-simulation vendors, such as SPEAG and 2Comu, are familiar with 3-D databases and can import STEP (Standard for the Exchange of Product Model Data), IGES (Initial Graphics Exchange Specification), DXF, and other mechanical-solid-modeling outputs (Figure 3). Once in the simulation program, the program meshes the solids with algorithms appropriate to the method.

Defining the mechanical shapes and dielectric constants of the physical design is only part of the EMC-analysis problem. When using a time-domain technique, you can just put the proper

Figure 2 This battleship is meshed for a 10-MHz analysis. A 10-GHz analysis would have a 100-times-finer mesh (courtesy CST).

Figure 3 You can import physical components from mechanical CAD packages and use the solid models in EM simulations (courtesy SPEAG).

time-domain waveforms on the ends of the traces. IBIS (I/O-buffer-information specification), a time-domain look-up table of driver-pin waveforms. can describe the rise and fall of a signal on a pin. You also must define the data on the pin; a PBRS (pseudorandom binary sequence) is often adequate for representing the spectral content of the signal on a functional product.

You can use IBIS-AMI (algorithmicmodeling interface) to define the preemphasis circuits and equalizers in the chips you are using, but it does not define the actual waveforms that will appear when your product is running. Typically, you just use a PBRS into the IBIS-AMI blocks. Meanwhile, your design may have hundreds of traces that might interact (**Figure 4**).

S parameters are the best way to represent the spectral content for the